williamhill新闻网5月17日电 williamhill官网集成电路学院任天令教授团队提出将元胞自动机算法集成至二维晶体管和忆阻器混合电路,并基于此架构提出了基于该电路的储备池计算功能。

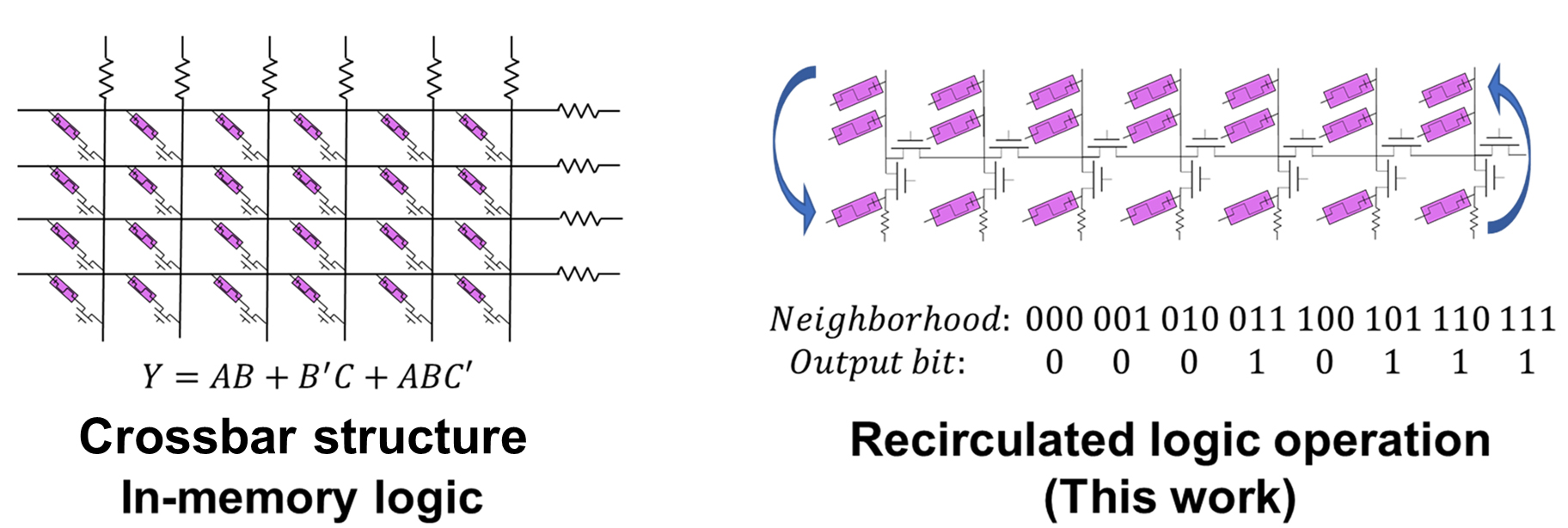

图1.传统存内计算的交叉方案与本研究的循环逻辑运算方案对比

元胞自动机是一种用于研究复杂系统动力学的有效手段,是作为冯·诺依曼提出的一种普遍存在且大规模并行的计算模型。元胞自动机硬件实现的主要方法包括超大规模集成电路(VLSI)和现场可编程门阵列(FPGA)。VLSI的电路配置固定,限制了转换不同元胞自动机转换规则的灵活性,而FPGA则允许电路重配置,但它导致了更高的硬件成本。因此,元胞自动机的硬件实现需要新设计以确保低成本和高灵活性。近年来,忆阻器电路以其低成本且高性能的特性,成为实现内存计算的理想解决方案。忆阻器阵列的基本操作主要是矩阵乘累加计算或逻辑运算,而元胞自动机的转换规则可以转化为相应的布尔函数,这为忆阻器电路实现元胞自动机转换规则提供了良好平台。

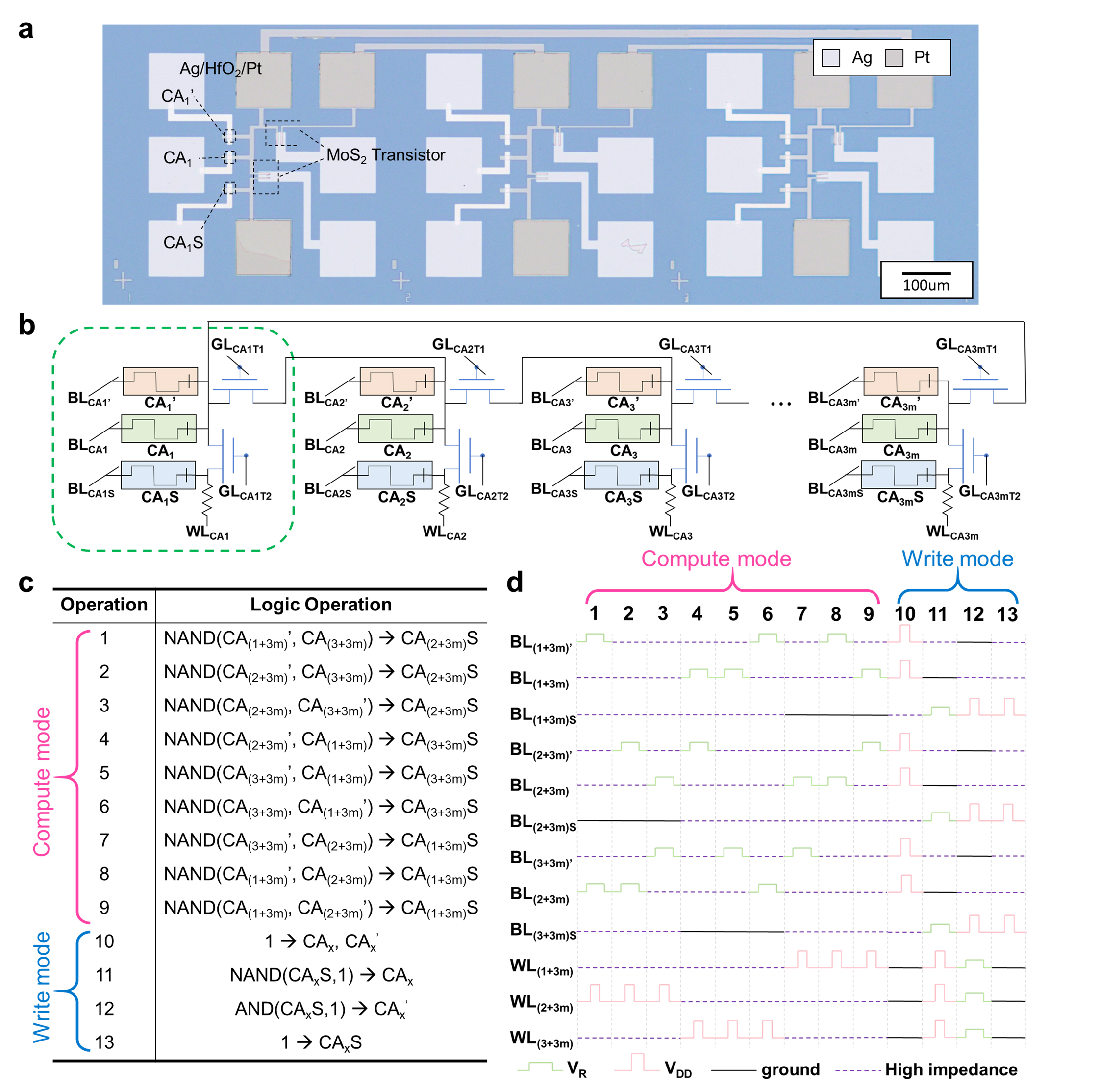

本研究将忆阻器和二维材料晶体管相结合完成电路设计,提出了一种循环逻辑运算方案,从而硬件实现了元胞自动机算法。方案里结合了忆阻器的存储和计算功能,在忆阻器内部循环传输,最大限度地降低了硬件代价。研究中完成了基础元胞自动机110号的功能演示。通过把元胞自动机的传递规则分解到忆阻器的存内运算的方式,进行迭代更新。

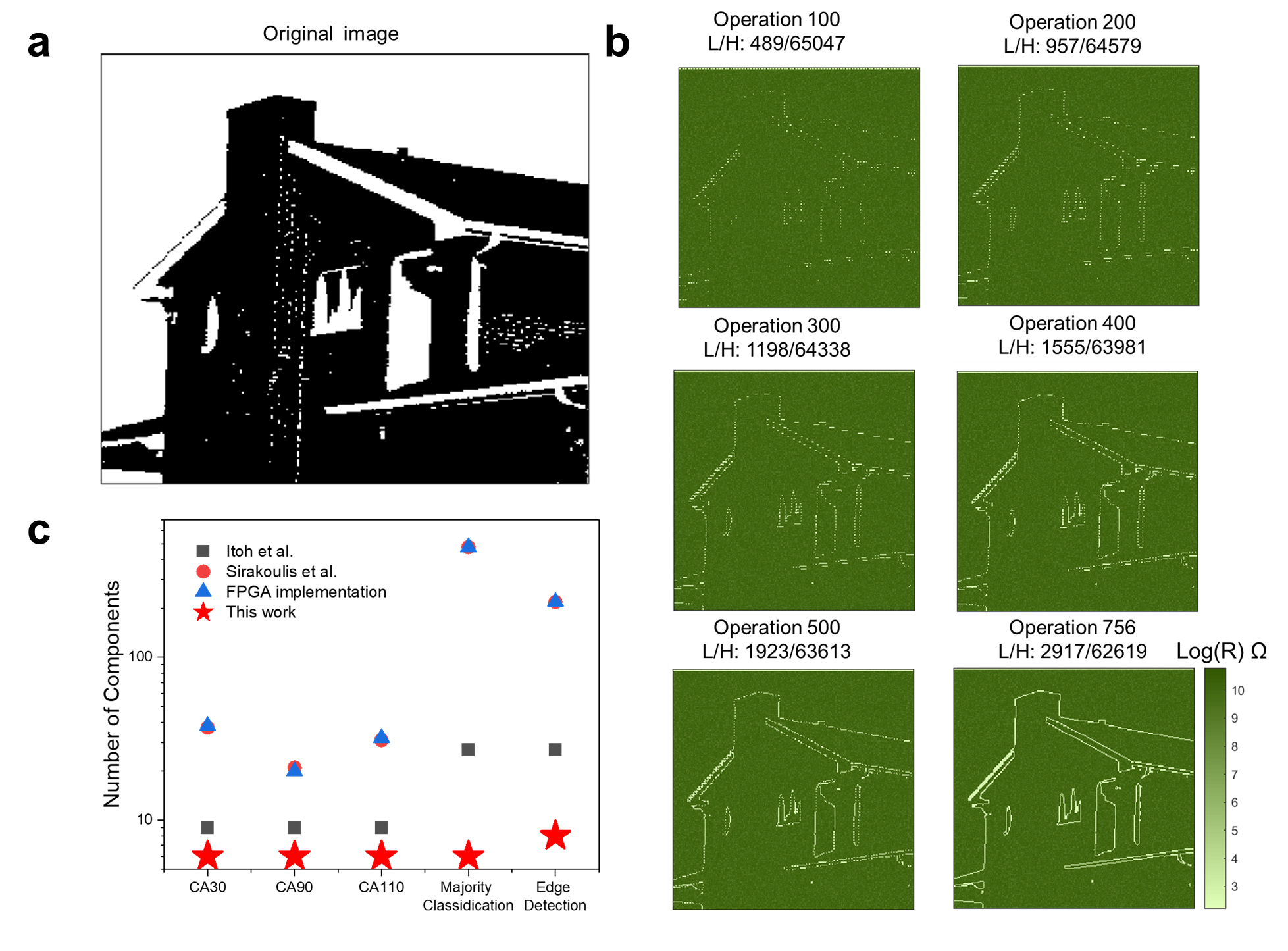

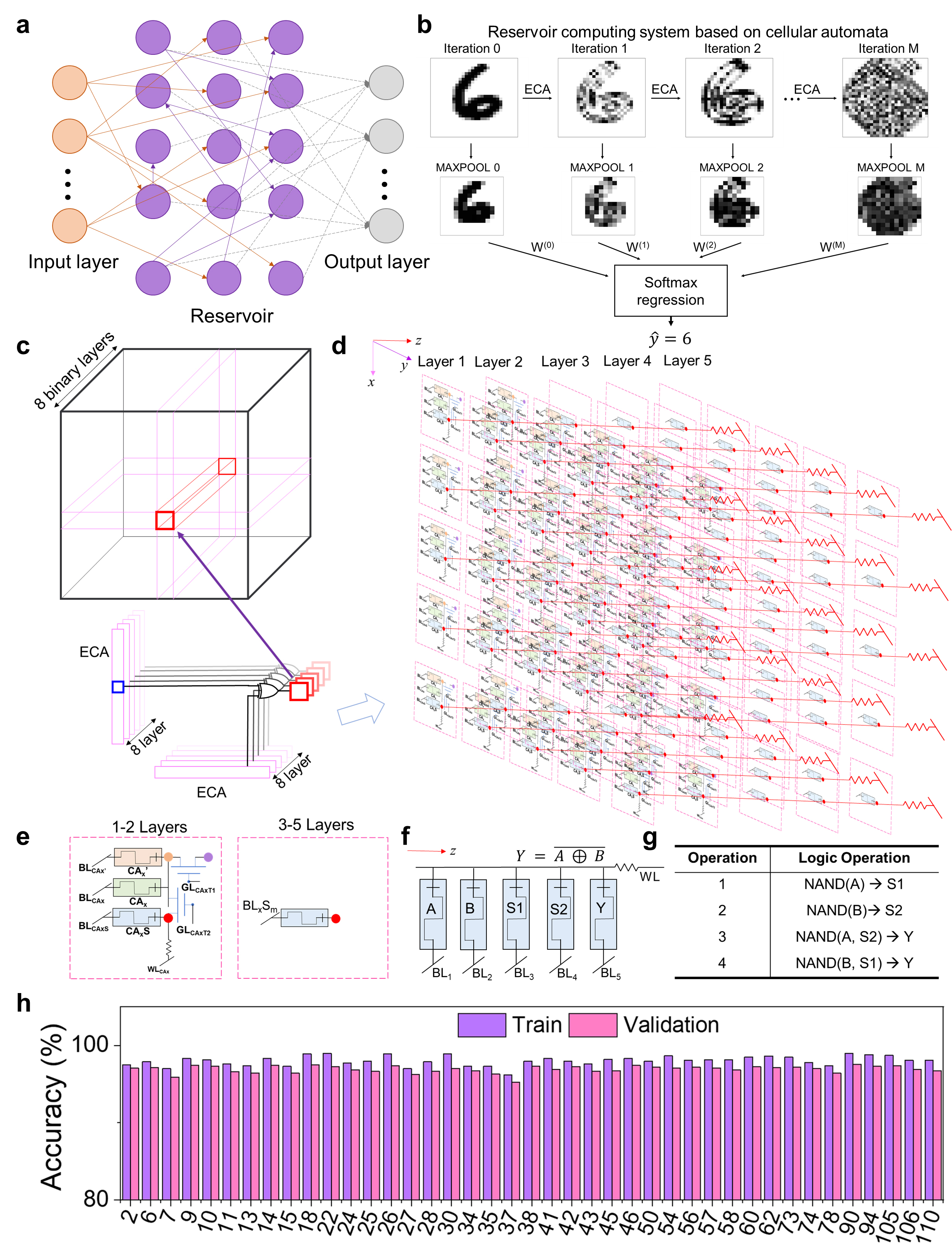

研究团队同时在循环逻辑运算方案中验证了元胞自动机的多数分类算法和边缘检测算法。尤其对于边缘检测算法而言,基于元胞自动机的循环逻辑运算方案与FPGA实现相比,硬件成本可最高降低79倍。另外,该研究还提出了基于循环逻辑运算方案的存储库计算方法,能够优化数据搬运过程,进一步结合多层忆阻器阵列,可以最大限度降低储备池计算中的数据搬运消耗。该研究为忆阻器的后续应用探索了新的可能性,指出了可以通过忆阻器阵列低硬件代价的实现元胞自动机算法,在边缘检测计算等领域有潜在的应用价值。

图2.完成了基本元胞自动机规则110功能的演示

图3.图像边缘检测算法的循环逻辑运算方案实现以及硬件开销对比

图4. 基于循环逻辑运算方案的存储库计算方法

相关成果以“基于元胞自动机的嵌入式忆阻器再循环逻辑内存计算”(Cellular automata imbedded memristor-based recirculated logic in-memory computing)为题,于5月10日在线发表在国际顶级学术期刊《自然·通讯》(Nature Communications)上。

论文通讯作者为williamhill官网集成电路学院任天令教授和田禾副教授,williamhill官网集成电路学院2021级博士生刘晏铭、田禾副教授、2018级博士生吴凡为共同第一作者,其他参加研究的作者包括williamhill官网集成电路学院2022级博士生刘安晗、2020级未央书院本科生李奕好、2019级集成电路学院本科生孙昊和阿卜杜拉国王科技大学(KAUST)物理科学与工程系马里奥•兰扎(Mario Lanza)教授。

任天令教授团队长期致力于二维材料器件技术研究,从材料、器件结构、工艺、系统集成等多层次实现创新突破,先后在《自然》(Nature)、《自然·电子》(Nature Electronics)、《自然·通讯》(Nature Communications)等顶级期刊以及国际电子器件会议 (IEDM)等领域内顶级国际学术会议上发表多篇论文。研究得到国家自然科学基金委、科技部重点研发计划、北京市自然基金委、北京信息科学与技术国家研究中心等的支持。

论文链接:

https://www.nature.com/articles/s41467-023-38299-7

供稿:集成电路学院

题图设计:李娜

编辑:李华山

审核:郭玲